?? 資源詳細信息

?? 溫馨提示:本資源由用戶 ibeikeleilei 上傳分享,僅供學習交流使用。如有侵權,請聯系我們刪除。

資源簡介

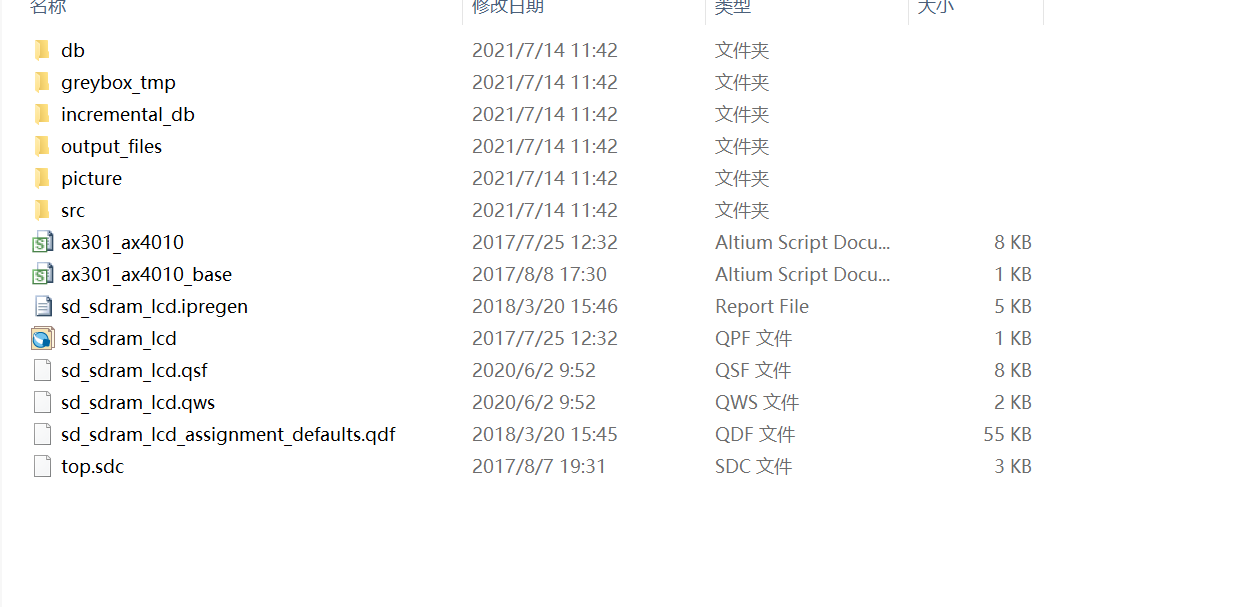

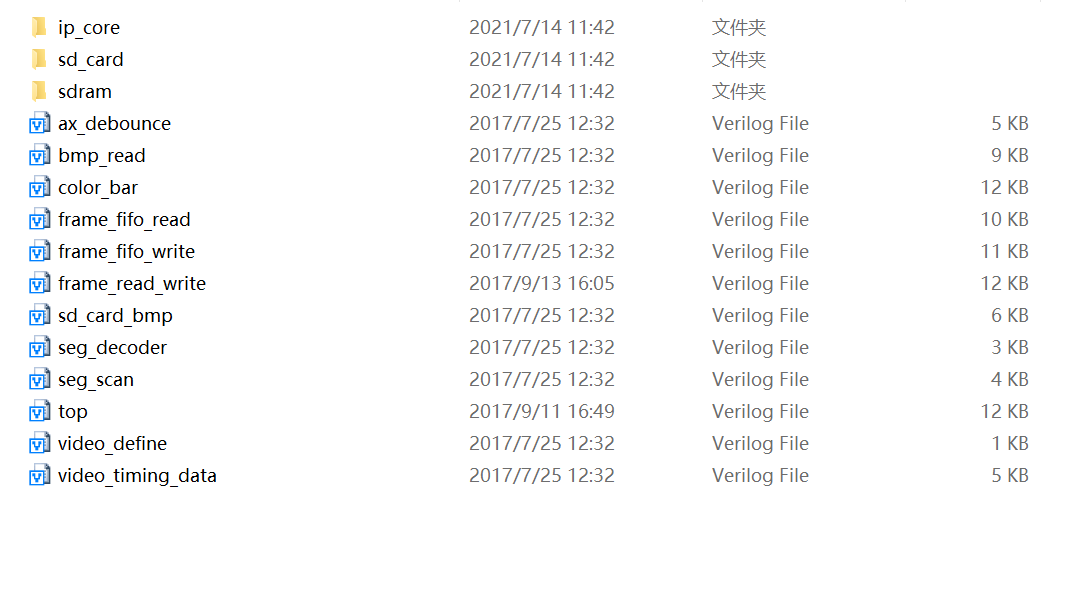

FPGA讀寫SD卡讀取BMP圖片通過LCD顯示例程實驗 Verilog邏輯源碼Quartus工程文件+文檔說明,FPGA型號Cyclone4E系列中的EP4CE6F17C8,Quartus版本17.1。

1 實驗簡介

在前面的實驗中我們練習了 SD 卡讀寫,VGA 視頻顯示等例程,本實驗將 SD 卡里的 BMP 圖

片讀出,寫入到外部存儲器,再通過 VGA、LCD 等顯示。

本實驗如果通過液晶屏顯示,需要有液晶屏模塊。

2 實驗原理

在前面的實驗中我們在 VGA、LCD 上顯示的是彩條,是 FPGA 內部產生的數據,本實驗將彩

條替換為 SD 內的 BMP 圖片數據,但是 SD 卡讀取速度遠遠不能滿足顯示速度的要求,只能先寫

入外部高速 RAM,再讀出后給視頻時序模塊顯示

module top(

input clk,

input rst_n,

input key1,

output [5:0] seg_sel,

output [7:0] seg_data,

output vga_out_hs, //vga horizontal synchronization

output vga_out_vs, //vga vertical synchronization

output[4:0] vga_out_r, //vga red

output[5:0] vga_out_g, //vga green

output[4:0] vga_out_b, //vga blue

output sd_ncs, //SD card chip select (SPI mode)

output sd_dclk, //SD card clock

output sd_mosi, //SD card controller data output

input sd_miso, //SD card controller data input

output sdram_clk, //sdram clock

output sdram_cke, //sdram clock enable

output sdram_cs_n, //sdram chip select

output sdram_we_n, //sdram write enable

output sdram_cas_n, //sdram column address strobe

output sdram_ras_n, //sdram row address strobe

output[1:0] sdram_dqm, //sdram data enable

output[1:0] sdram_ba, //sdram bank address

output[12:0] sdram_addr, //sdram address

inout[15:0] sdram_dq //sdram data

);

parameter MEM_DATA_BITS = 16 ; //external memory user interface data width

parameter ADDR_BITS = 24

立即下載此資源

資源說明

下載說明

- 下載需消耗 2積分

- 24小時內重復下載不扣分

- 支持斷點續傳

- 資源永久有效

使用說明

- 下載后用解壓軟件解壓

- 推薦 WinRAR 或 7-Zip

- 如有密碼請查看說明

- 解壓后即可使用

積分獲取

- 上傳資源獲得積分

- 每日簽到免費領取

- 邀請好友注冊獎勵

- 查看詳情 →